語(yǔ)音識(shí)別與嵌入式電子電路設(shè)計(jì)圖集錦

語(yǔ)音識(shí)別技術(shù)作為人機(jī)交互的關(guān)鍵接口,正日益廣泛應(yīng)用于智能家居、可穿戴設(shè)備、工業(yè)控制和消費(fèi)電子等領(lǐng)域。其核心是將聲音信號(hào)轉(zhuǎn)化為可處理的數(shù)字信號(hào),進(jìn)而識(shí)別和理解語(yǔ)音內(nèi)容。這一過(guò)程離不開(kāi)精心設(shè)計(jì)的硬件電路,尤其是嵌入式系統(tǒng)和集成電路的支持。本文將聚焦于語(yǔ)音識(shí)別相關(guān)的電路設(shè)計(jì),特別是嵌入式類(lèi)電子電路與集成電路的設(shè)計(jì)要點(diǎn)和圖例集錦。

一、語(yǔ)音識(shí)別系統(tǒng)的基本硬件架構(gòu)

一個(gè)典型的語(yǔ)音識(shí)別硬件系統(tǒng)通常包含以下幾個(gè)核心部分:麥克風(fēng)及前置放大電路、模數(shù)轉(zhuǎn)換器(ADC)、主控處理單元(通常為微控制器MCU或數(shù)字信號(hào)處理器DSP)、存儲(chǔ)器以及必要的電源管理電路。其信號(hào)流程為:聲音通過(guò)麥克風(fēng)轉(zhuǎn)換為微弱的模擬電信號(hào),經(jīng)過(guò)前置放大器放大和濾波后,由ADC轉(zhuǎn)換為數(shù)字信號(hào),最后交由主控單元進(jìn)行特征提取和模式識(shí)別算法處理。

二、關(guān)鍵電路模塊設(shè)計(jì)圖例與解析

- 麥克風(fēng)輸入與前置放大電路

- 駐極體麥克風(fēng)接口電路:通常需要一個(gè)偏置電阻(如2.2kΩ)為麥克風(fēng)內(nèi)部的場(chǎng)效應(yīng)管(FET)提供工作電壓,并串聯(lián)一個(gè)耦合電容(如1μF)以隔直流通交流。

- 運(yùn)算放大器放大電路:采用同相或反相放大結(jié)構(gòu)。例如,使用低噪聲運(yùn)放(如TI的OPA1612)構(gòu)建增益可調(diào)的放大電路,并配合高通濾波器(截止頻率約100Hz)濾除環(huán)境低頻噪聲。電路圖中需明確顯示電阻、電容的取值和運(yùn)放的供電引腳連接。

- 模數(shù)轉(zhuǎn)換(ADC)電路

- 對(duì)于語(yǔ)音信號(hào)(帶寬通常為300-3400Hz),需選用采樣率不低于8kHz的ADC。嵌入式系統(tǒng)中常使用MCU內(nèi)置的ADC模塊。若需外置,可選擇Σ-Δ型ADC以獲得高信噪比。電路設(shè)計(jì)需注意模擬電源的濾波,通常在ADC電源引腳附近放置0.1μF和10μF的去耦電容。模擬地與數(shù)字地的單點(diǎn)連接也是設(shè)計(jì)關(guān)鍵,通常在原理圖中用磁珠或0Ω電阻標(biāo)識(shí)。

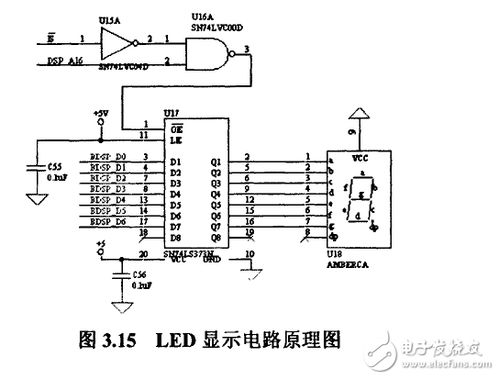

- 主控單元及外圍電路

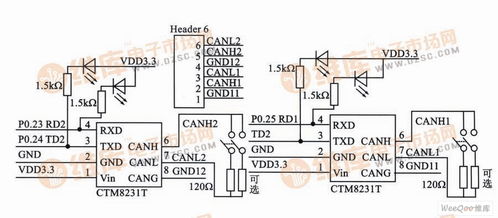

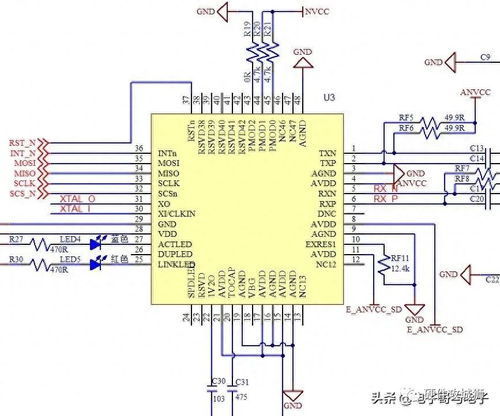

- 以ARM Cortex-M系列MCU(如STM32F4)為核心的嵌入式系統(tǒng)是常見(jiàn)選擇。電路圖需包含:MCU最小系統(tǒng)(晶體振蕩器電路、復(fù)位電路、啟動(dòng)模式配置電路)、與ADC的接口(可能是SPI或I2C)、用于存儲(chǔ)語(yǔ)音模型的Flash或EEPROM存儲(chǔ)器接口電路,以及用于調(diào)試的SWD/JTAG接口電路。

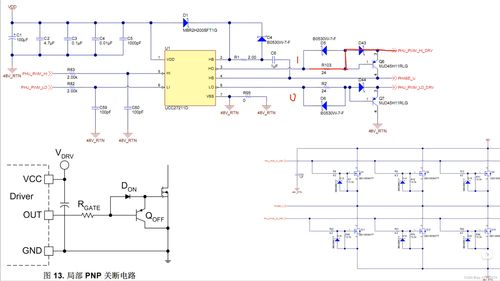

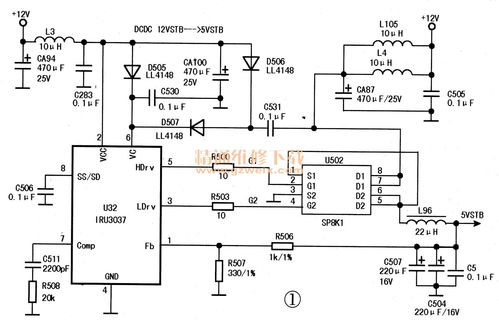

- 電源管理電路:由于語(yǔ)音識(shí)別系統(tǒng)可能由電池供電,設(shè)計(jì)高效的DC-DC降壓電路(如使用TI的TPS62740)或低壓差線性穩(wěn)壓器(LDO)為模擬和數(shù)字部分分別供電,并在原理圖中明確標(biāo)示。

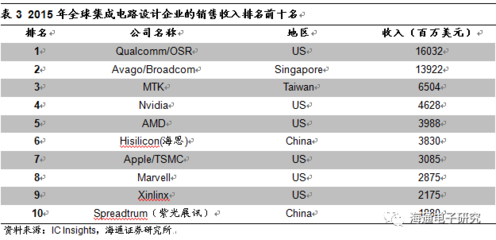

- 專(zhuān)用語(yǔ)音識(shí)別集成電路

- 對(duì)于低復(fù)雜度或始終在線的語(yǔ)音喚醒應(yīng)用,常采用專(zhuān)用集成電路。例如,科大訊飛的XFS5152芯片或Sensory的Trigger-Speech系列。這些芯片通常集成前置放大器、ADC、語(yǔ)音處理算法和簡(jiǎn)單的控制接口。設(shè)計(jì)圖需重點(diǎn)展示其典型應(yīng)用電路:麥克風(fēng)輸入引腳、I2C/SPI/UART與控制MCU的通信線路、電源引腳的去耦設(shè)計(jì),以及可能的音頻輸出電路。

三、嵌入式語(yǔ)音識(shí)別電路設(shè)計(jì)要點(diǎn)

- 低功耗設(shè)計(jì):在電路圖設(shè)計(jì)中,需考慮使用功耗低的元器件,并規(guī)劃電源域,使系統(tǒng)在非活躍時(shí)段能進(jìn)入睡眠模式,僅由語(yǔ)音喚醒電路值守。

- 抗噪聲設(shè)計(jì):除了電路中的濾波設(shè)計(jì),在PCB布局時(shí),模擬信號(hào)走線應(yīng)盡可能短,并用地平面進(jìn)行屏蔽,遠(yuǎn)離數(shù)字噪聲源(如時(shí)鐘線)。

- 算法與硬件協(xié)同:電路設(shè)計(jì)需與將要運(yùn)行的語(yǔ)音識(shí)別算法(如動(dòng)態(tài)時(shí)間規(guī)整DTW或深度學(xué)習(xí)模型)的運(yùn)算需求相匹配,確保MCU性能、內(nèi)存和接口資源充足。

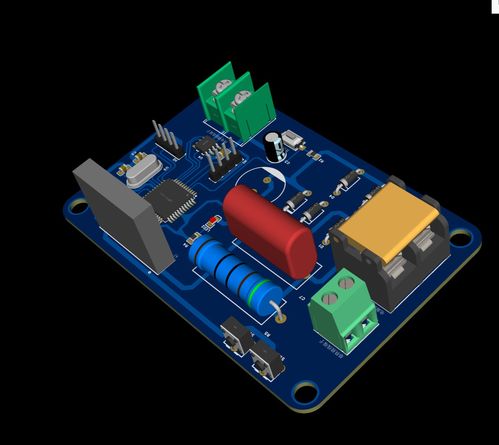

四、設(shè)計(jì)圖集錦概覽

在實(shí)際工程中,完整的語(yǔ)音識(shí)別嵌入式電路設(shè)計(jì)圖是一套包含原理圖、PCB布局圖乃至結(jié)構(gòu)框圖的文檔集合。原理圖應(yīng)層次清晰,模塊化繪制;PCB圖則需體現(xiàn)良好的電磁兼容性布局。

語(yǔ)音識(shí)別電路設(shè)計(jì)是軟硬件結(jié)合的典范。從精確的模擬前端到高效的數(shù)字處理,再到專(zhuān)用的集成電路方案,每一部分的設(shè)計(jì)都直接影響識(shí)別的準(zhǔn)確度和系統(tǒng)的整體效能。工程師在參考現(xiàn)有設(shè)計(jì)圖集時(shí),需深刻理解其原理,并根據(jù)具體應(yīng)用場(chǎng)景(如成本、功耗、識(shí)別率要求)進(jìn)行優(yōu)化和創(chuàng)新,方能設(shè)計(jì)出穩(wěn)定可靠的語(yǔ)音交互硬件平臺(tái)。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://m.pyspider.cn/product/58.html

更新時(shí)間:2026-02-22 00:19:01